## Composants séquentiels

Bilan de l'offre commerciale

Le reste du combinatoire (add, alu, comparateur)

Mémoires, Bascules, Registre à décalage universel

Compteurs asynchrones et synchrones

Méthode de marcus

Cascadage des compteurs (ENT et ENP)

# Les familles de circuits logiques

Circuits Standards (combinatoires et séquentiels)

Logique cablée (glue logique)

Micro-processeurs, micro-controleurs, DSP (2A) Circuits périphériques de micro-processeurs (2A) Circuits mémoires (2A)

Logique programmée (à programme enregistré)

ASICs (Application Specific Integrated Circuit) (2A)

Logique programmable

Cellules précaractérisées, Circuits prédiffusés

Circuit à la demande (full custom)

#### Vocabulaire

Intégration : SSI, MSI, LSI, VLSI, ... (Scale of Integration)

Technologie: TTL (Transistor Transistor Logic)

CMOS (Complementary Metal Oxyd SC)

**ECL**

I2L

**BiCMOS**

• • •

Sous familles: TTL-LS, TTL-ALS, TTL-S ...

CMOS-4000, CMOS-HCT, CMOS-AHCT...

# Offre commerciale: glue logic

```

(rubriques du « data book »)

Gates (inv, nand, nor, and, or, xor, xnor)

Multiplexors (Quad-2-in, Dual-4-in, 8-in ..)

Decoders, Demultiplexors (Dual 1 of 4, 1 of 8,BCD-7seg ...)

Comparators (4 bits, 8 bits)

Arithmetics (4 bit ALU, Carry generator, 6 bit multiplier ...)

Latches (RS, D)

Flip-flops (D, JK, Dual, Quad ...)

Counters (Synchronous, asynchronous, up/down ...)

Shift registers (Serial In-Parallel Out, General ...)

Miscellaneous (priority encoder, error detection, arbitror ...)

« analogique » (buffer, driver, tranceivers ..)

```

#### Le reste du combinatoire (1)

#### **Additionneurs**

| a b | S | r |

|-----|---|---|

| 0 0 | 0 | 0 |

| 0 1 | 1 | 0 |

| 10  | 1 | 0 |

| 1 1 | 0 | 1 |

$$S = a \oplus b$$

$$r = a.b$$

Demi-additionneur (addition modulo 2)

$$\begin{array}{c|cccc} a \ b \ r_i & S \ r_o \\ \hline 0 \ 0 \ 0 & 0 \ 0 \\ 0 \ 1 \ 0 & 1 \ 0 \\ 1 \ 0 \ 0 & 1 \ 0 \\ 1 \ 1 \ 0 & 1 \\ 1 \ 0 \ 1 & 0 \ 1 \\ 1 \ 1 \ 1 & 1 \ 1 \\ \end{array}$$

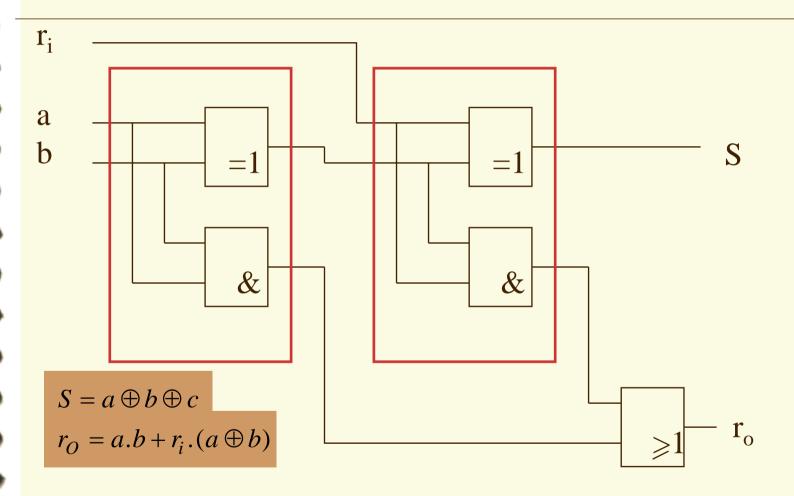

$$S = a \oplus b \oplus c$$

$$r_0 = a.b + r_i.(a \oplus b)$$

Additionneur complet

## Additionneur: architecture

12/09/2005

Yannick HERVE (ENSPS)

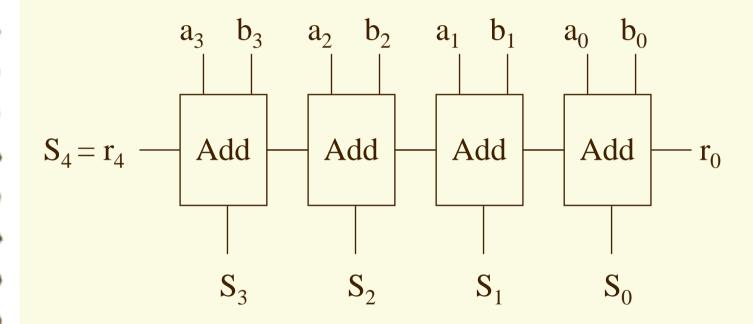

# Additionneur n bits: propagation

Avantage: simplicité, modularité

Inconvénient : temps de calcul dépend de n

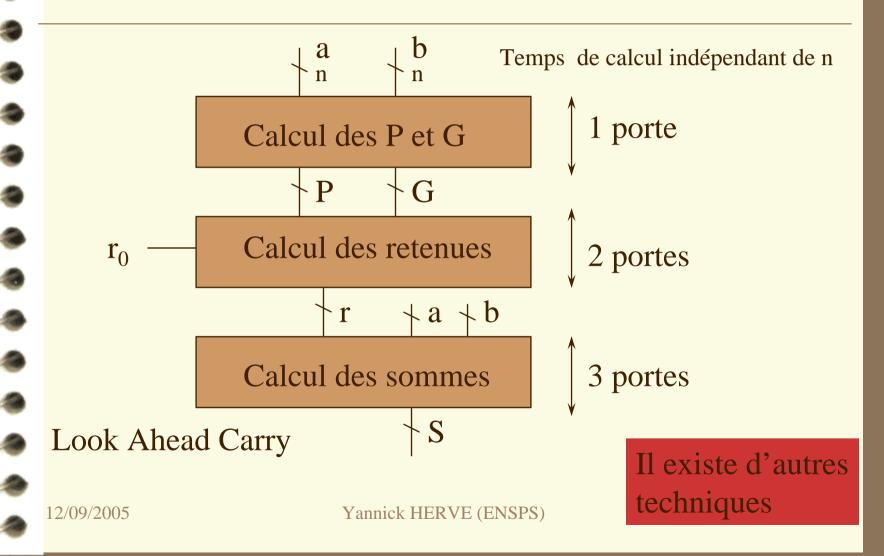

## Additionneur n bits: anticipation

Remarque générale : les architecture à accumulation de temps de propagation sont néfastes à la croissance des systèmes

Les P<sub>i</sub> et G<sub>i</sub> ne dépendent que des a<sub>i</sub> et b<sub>i</sub>

## Anticipation (2)

Equations de calcul des retenues

$$r_1 = G_0 + r_0.P_0$$

$$r_2 = G_1 + r_1.P_1 = G_1 + G_0.P_1 + r_0.P_0.P_1$$

$$r_3 = G_2 + G_1.P_2 + G_0.P_1.P_2 + r_0.P_0.P_1.P_2$$

• • • •

## Anticipation (3): architecture

## Applications: 74181

74181 ALU 4 bits

Architecture interne de type «look-ahead»

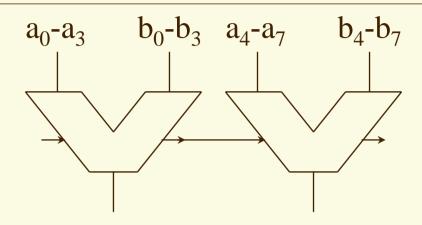

Propagation = dégradation des performances temporelles

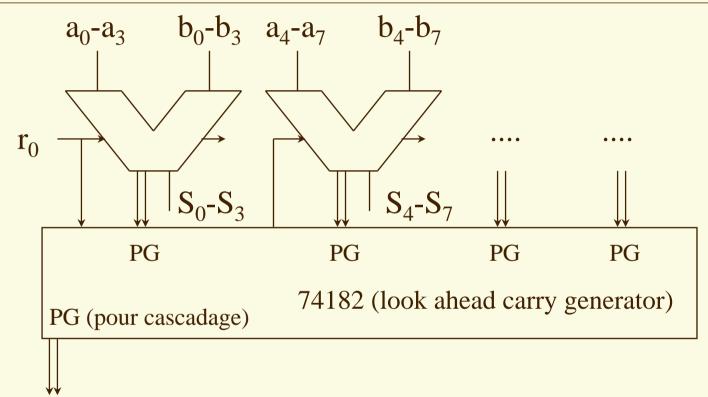

#### Application: 74181+74182

Un 74182 peut prendre en charge quatre 74181 Ils sont cascadables en arborescence

#### Comparateur (1)

a/ Egalité de 2 nombres binairesb/ Le plus grand ou le plus petit

#### Principes:

- Soustraction A-B > 0 implique A > BA-B = 0 implique A = B

- Comparaison bit à bit (dans les CI du commerce)

sur n bits :

$$A > B$$

si  $A_{n-1} > B_{n-1}$

ou si  $A_{n-1} = B_{n-1}$  et  $A_{n-2} > B_{n-2}$

ou si  $A_{n-1} = B_{n-1}$  et  $A_{n-2} = B_{n-2}$  et  $A_{n-3} > B_{n-3}$

ou ...

Exemple: A=111010 B=110010

## Comparateur (2)

Comparateur d'égalité :  $A = a_3 a_2 a_1 a_0$   $B = b_3 b_2 b_1 b_0$

$$A = B \text{ si } a_3 = b_3 \text{ et } a_2 = b_2 \text{ et } a_1 = b_1 \text{ et } a_0 = b_0$$

Fonction associée:

$$(a_3 \oplus b_3).(a_2 \oplus b_2).(a_1 \oplus b_1).(a_0 \oplus b_0)$$

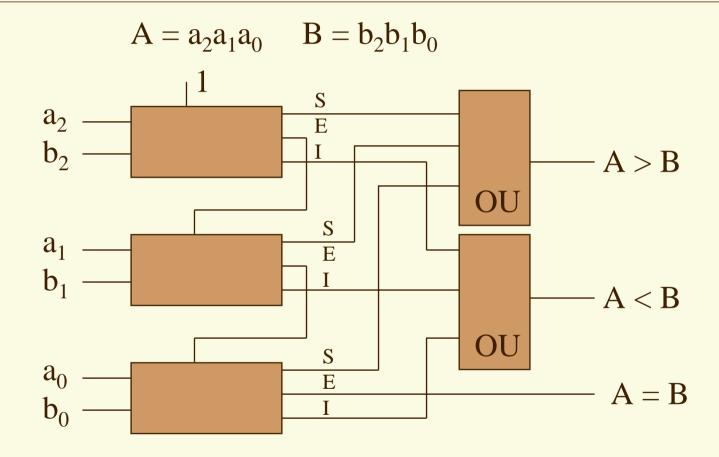

## Comparateur complet

Comparateur en cascade OU Comparateur parallèle

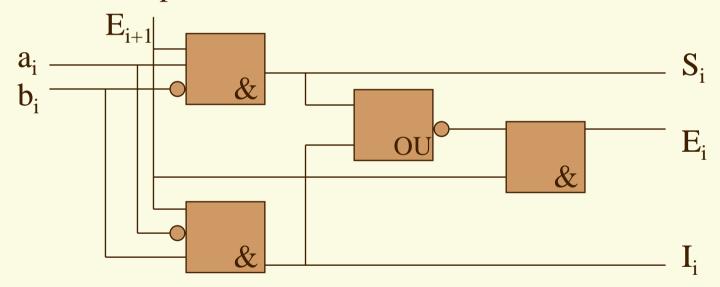

Comparateur en cascade : cellule de base

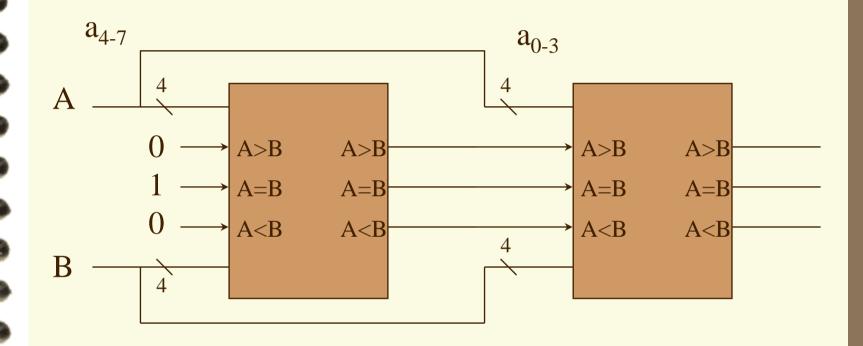

#### Comparateur en cascade

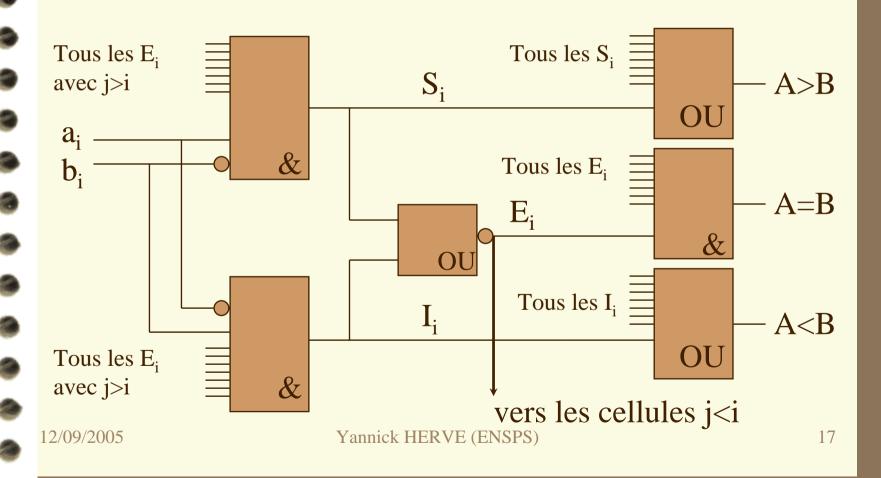

## Comparateur parallèle (1)

Cellule de base et architecture : tps de calcul indépendant de n

## Comparateur: 7485

Cascade série (cascade parallèle possible à partir de 10 bits)

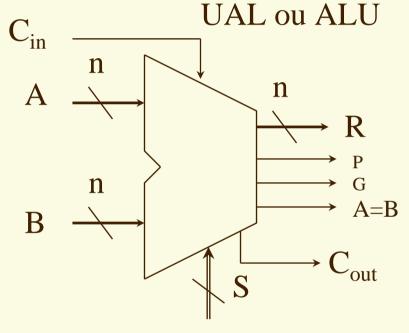

## Unité arithmétique et logique

5 fils de prog (S) 32 fonctions

16 fct logiques(bit à bit)

$$R = \overline{A}, R = \overline{A + B}, R = \overline{A}.B$$

$R = 0, R = \overline{A.B}, R = \overline{A} + B$

....

16 fct arithmét. (nombres)

$$R = A, R = A + B, R = \overline{A} + B$$

$R = -1, R = A + A. \overline{B}, R = A - B - 1$

Anecdote: 74181

ALU 4bits = 63 portes

## Composants séquentiels : base

Mémoires, Bascules (voir le cours précédent)

RS, DT / D-edge, JK

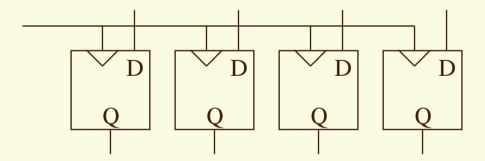

Registre : ensemble de D-edge avec la même horloge

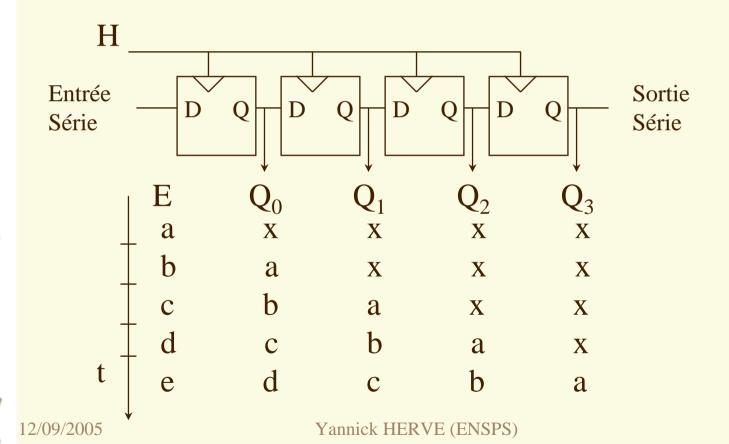

## Registre à décalage

Registre + connexions + combinatoire de gestion

21

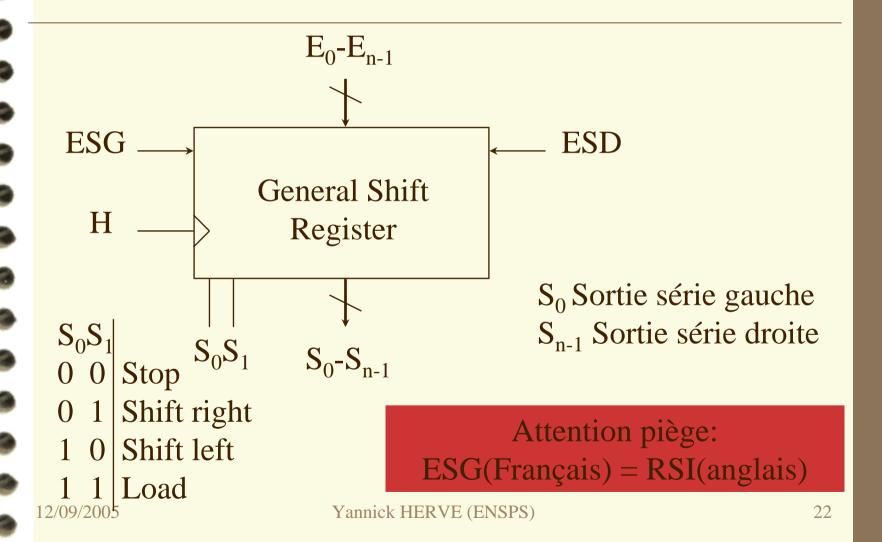

#### Registre universel

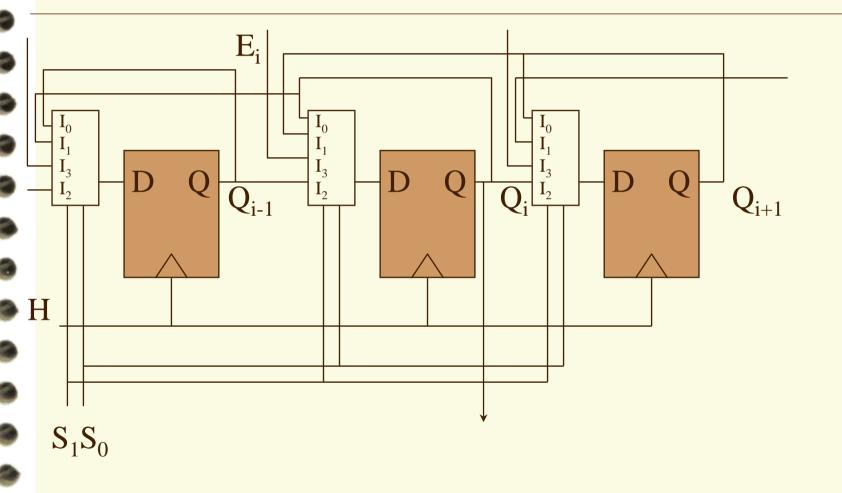

# Registre universel: architecture

#### Les compteurs

1<sup>er</sup> compteur =1932

Rappel: 1<sup>ère</sup> bascule =1906.

Définition : N sorties qui parcourent un code au rythme d'une horloge (!! pas forcément comptage naturel)

Utilité : comptage d'événements suite d'états

• • • •

Deux techniques: Mise en cascade de diviseurs par deux

Comptage asynchrone

Calcul de transition

Comptage synchrone

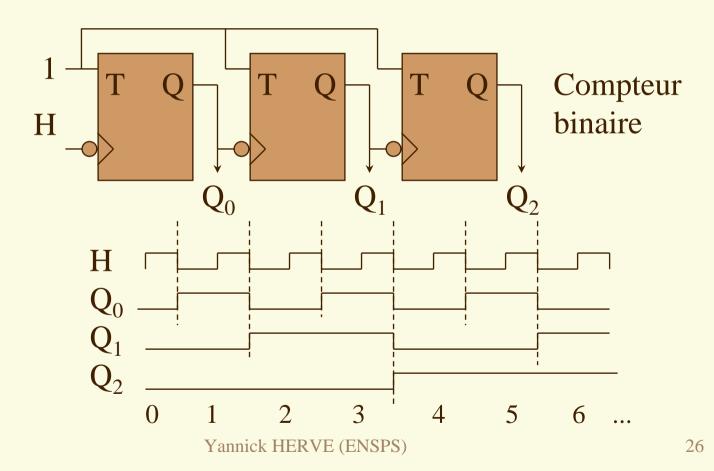

#### Compteurs asynchrones: principe (1)

Cascade de diviseurs de fréquence par deux sur fronts montants

12/09/2005

Yannick HERVE (ENSPS)

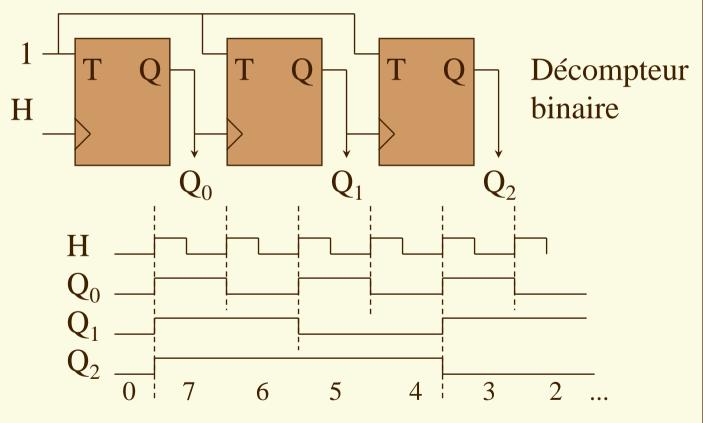

#### Compteurs asynchrones: principe (2)

Cascade de diviseurs de fréquence sur fronts descendants

12/09/2005

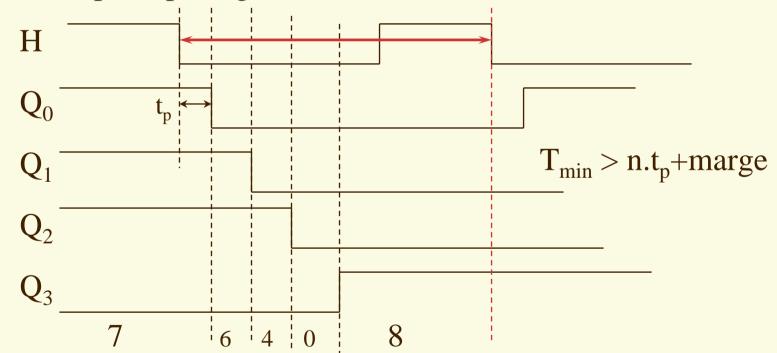

#### Compteurs asynchrones : problèmes

Accumulation des temps de propagation

Exemple: passage de 7 à 8

Si n bascules changent d'état : n-1 états transitoires

12/09/2005

Yannick HERVE (ENSPS)

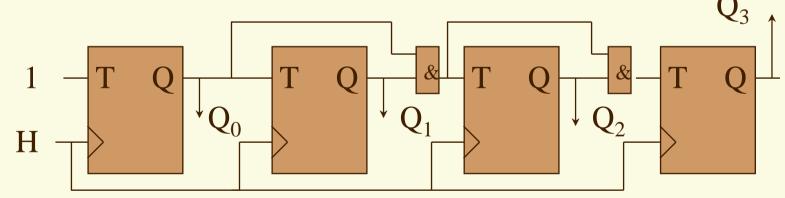

## Compteurs synchrones (1)

Remarque : en comptage binaire un bit change d'état

si tous les bits précédents sont à 1 (ex:0111 à 1000)

Synchrone : même horloge pour toutes les bascules

|   | $t_{00}$ | $t_{01}$ | t <sub>10</sub> | t <sub>11</sub> |

|---|----------|----------|-----------------|-----------------|

| T | 0        | 1        | 1               | 0               |

Compteur synchrone à report série

12/09/2005

Yannick HERVE (ENSPS)

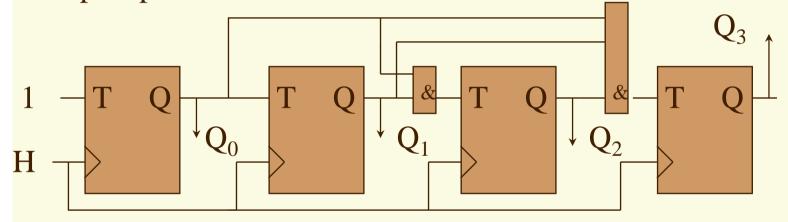

## Compteur synchrones (2)

Report Série :  $T_{min} > T_p(bascule) + (n-2) * T_p(porte ET)$

Report parallèle:

$$T_{min} > T_p(bascule) + T_p(porte ET)$$

Pour n bits il faut 1 porte ET à n-1 entrées

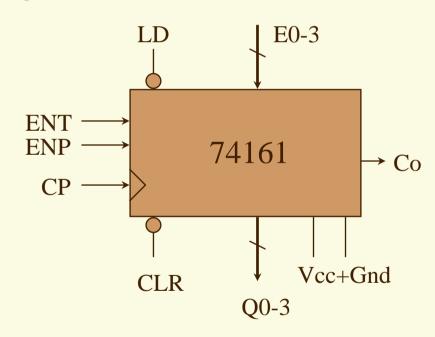

#### Présentation du 74161

74161 compteur intégré synchrone 4 bits binaire programmable cascadable de la famille TTL (16 broches (pins))

CP: horloge (front montant)

Q0-3 : sorties du compteur

E0-3 : entrées parallèles (de prog)

CLR: RAZ asynchrone active à 0

Co LD: chargt parallèle synchrone actif au niveau bas

prioritaire sur le comptage

ENP/ENT: autorisation de comptage

comptage si ENP.ENT=1

Co : retenue =1 si  $Q_3Q_2Q_1Q_0$ ENT=1

(ENT agit sur Co en asynchrone)